# CFP2/CFP2-ACO Kit Interconnects' Manual <a href="https://www.multilaneinc.com">www.multilaneinc.com</a>

# MSA Compliant CFP2 4x25G Gb/s Passive Host

**ML4027**

## MSA Compliant CFP2 4x25G Gb/s Retimed Loopback Module

ML4029

# 10 x 10 GB/s CFP2 Breakout Module

**ML4028**

# MSA Compliant CFP2 10x10G Gb/s Passive Host

**ML4042**

## MSA Compliant CFP2 10x10G Gb/s Passive Loopback Module

**ML4030**

## MSA Compliant CFP2 10x10G Gb/s Retimed Loopback Module

**ML4043**

MSA Compliant CFP2-ACO 4x25G Gb/s Passive Host

**ML4027-ACO**

MSA Compliant CFP2-ACO 4x25G Gb/s Breakout Module

**ML4028-ACO**

MSA Compliant CFP2-ACO 4x25G Gb/s Passive Host

**ML4030-ACO**

User Manual for the CFP2 and CFP2-ACO 100 Gb/s Electrical Loopback Modules, CFP2 and CFP2-ACO Host & Breakout Module

User Manual Version 0.0.6

Sept 11<sup>th</sup>, 2014

Product Model Numbers: ML4027, ML4027-ACO, ML4028, ML4028-ACO, ML4029, ML4030, ML4030-ACO, ML4042, ML4043

Copyright © MultiLane SAL. All rights reserved. Licensed software products are owned by MultiLane SAL or its suppliers and are protected by United States copyright laws and international treaty provisions.

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subparagraph (c)(1)(ii) of the Rights in Technical Data and Computer Software clause at DFARS 252.227-7013, or subparagraphs (c)(1) and (2) of the Commercial Computer Software -- Restricted Rights clause at FAR 52.227-19, as applicable.

MultiLane S.A.L., Houmal Technology Park, Houmal.

ML4027, ML4027-ACO, ML4028, ML4028-ACO, ML4029, ML4030, ML4030-ACO, ML4042 and ML4043 hardware are registered trademarks of MultiLane, S.A.L.

## **Contents**

|     |            | afety Summary                                           |             |

|-----|------------|---------------------------------------------------------|-------------|

|     |            | Toolsof Terms/ Acronyms                                 |             |

|     |            | or rems/ Actoryms                                       |             |

| 4.1 | Abo        | ut This Manual                                          | 1           |

| 5.  | Products 1 | Description                                             | 12          |

|     |            | 5.1                                                     | Overview 12 |

| 6.  | CFP2 Loc   | ppback Modules User Guide Manual                        | 13          |

| 6.1 | ML         | 4029- CFP-2 4x25G Retimed Loopback Module Key Features  | 13          |

|     | 6.1.1      | Benefits                                                | 13          |

|     | 6.1.2      | LED Indicator                                           | 13          |

|     | 6.1.3      | Applications                                            | 13          |

|     | 6.1.4      | Operation Conditions                                    | 14          |

| 6.2 | . ML       | 4030-CFP-2 10x10G Passive Loopback Module Key Features  | 14          |

|     | 6.2.1      | Benefits                                                |             |

|     | 6.2.2      | LED Indicator                                           | 15          |

|     | 6.2.3      | Applications                                            | 15          |

|     | 6.2.4      | Operation Conditions                                    | 15          |

| 6.3 | MI.        | 4043-CFP-2 10x10G Retimed Loopback Module Key Features  | 1           |

|     | 6.3.1      | Benefits                                                |             |

|     | 6.3.2      | LED Indicator                                           | 16          |

|     | 6.3.3      | Applications                                            | 16          |

|     | 6.3.4      | Operation Conditions                                    | 16          |

| 6.4 | Dluc       | gging the CFP2 Loopback module into the Host            | 14          |

|     |            |                                                         |             |

| 6.5 |            | eral Description                                        |             |

|     | 6.5.1      | Overview of CFP management Interface                    |             |

|     | 6.5.2      | High Speed Signals                                      | 17          |

| 6.6 | Inte       | rface Architecture                                      | 18          |

| 7.  |            | ppback Modules Functional Description                   |             |

| 7.1 | CFF        | 2 Common Specifications (for ML4029, ML4030 and ML4043) |             |

|     | 7.1.1      | CFP Initialization sequence                             | 19          |

|     | 7.1.2      | MDIO SIGNALS, addressing and frame structure            | 20          |

|     | 7.1.3      | CFP Register Set                                        | 22          |

|    | 7.1.4 | User NVR Restore and Save Functions (0xA004)             |     | 23              |

|----|-------|----------------------------------------------------------|-----|-----------------|

|    | 7.1.5 | PRG_ALRMs                                                |     | 23              |

|    | 7.1.6 | Temperature Monitoring                                   |     | 24              |

|    | 7.1.7 | Insertion Counter                                        |     | 25              |

|    | 7.1.8 | Module Control and Status Registers                      |     | 25              |

| 7. | .2    | ML4029 CFP2 4x25G Retimed Loopback Additional Functions  |     | 26              |

|    | 7.2.1 | PRBS Generator                                           |     | 26              |

|    | 7.2.2 | PRBS Checker                                             |     | 26              |

|    | 7.2.3 | MSA Compliant Host Lane PRBS Control                     |     | 26              |

|    | 7.2.4 | Error Injection                                          |     | 27              |

|    | 7.2.5 | EyeScan Capability                                       |     | 27              |

|    | 7.2.6 | Bathtub Curve Measurement                                |     | 27              |

| 7. | .3    | ML4030 CFP2 10x10G Passive Loopback Additional Functions |     | 28              |

|    | 7.3.1 |                                                          |     |                 |

|    | 7.3.2 | Cut-Off Temperature                                      |     | 28              |

|    | 7.3.3 | RX_LOS                                                   |     | 28              |

| 7. | 4     | ML4043 CFP2 10x10G Retimed Loopback Additional Functions |     | 29              |

|    | 7.4.1 |                                                          |     |                 |

|    | 7.4.2 | Input and DFE Adaptation                                 |     | 29              |

|    | 7.4.3 | Loss of Signal (LOS) Detection                           |     | 29              |

|    | 7.4.4 | Clock Recovery Unit                                      |     | 29              |

|    | 7.4.5 | Host Lane PRBS Checker                                   |     | 29              |

| 8. | ML40  | 027/ML4027-ACO/ML4042 CFP2 Host Programming Manual       |     | 30              |

|    |       |                                                          | 8.1 | Introduction 30 |

|    | 8.1.1 | Key Features                                             |     | 30              |

|    | 8.1.2 | Benefits                                                 |     | 32              |

|    | 8.1.3 | Applications                                             |     | 32              |

|    | 8.1.4 | Software Capabilities                                    |     | 32              |

|    | 8.1.5 | Power Requirements                                       |     | 32              |

| 8. | .2    | Package Contents                                         |     | 33              |

|    |       |                                                          |     |                 |

Installation 34

8.3

|     | 8.3.   | 1      | USB Driver Installation on Windows XP         |        |              | . 34     |

|-----|--------|--------|-----------------------------------------------|--------|--------------|----------|

| 8   | 3.5    | Com    | munication Window                             |        |              | 36       |

| 8   | 3.6    | Grap   | phical User Interface Section                 |        |              | 38       |

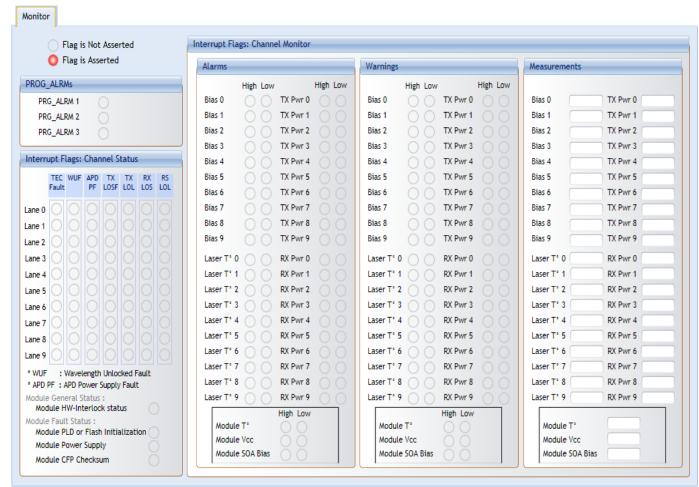

|     | 8.6.   | 1      | Monitor                                       |        |              | . 39     |

|     | II- N  | /lodul | e Fault and Status                            |        |              | . 42     |

|     | I-Ne   | twor   | k Lane Alarms and Warnings                    |        |              | . 43     |

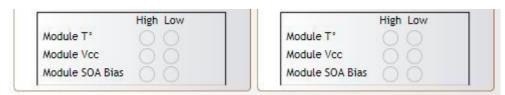

|     | II- N  | ⁄lodul | e Alarms and Warnings                         |        |              | . 44     |

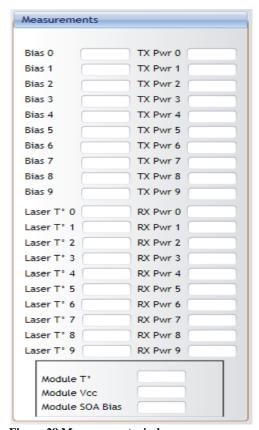

|     | III- N | Meas   | urements                                      |        |              | . 45     |

|     | 8.6.   | 2      | Interrupt Masks                               |        |              | . 46     |

|     | 8.6.   | 3      | Module Command/Setup                          |        |              | . 47     |

|     | III -  | Modu   | ıle Bi-/Uni Directional Operating mode select |        |              | . 50     |

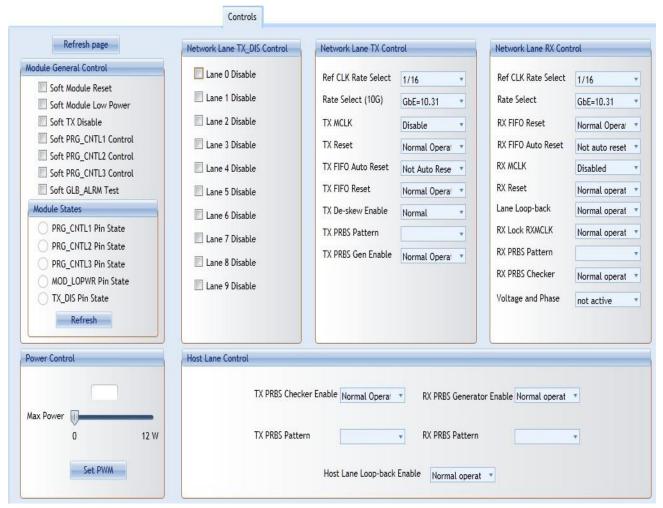

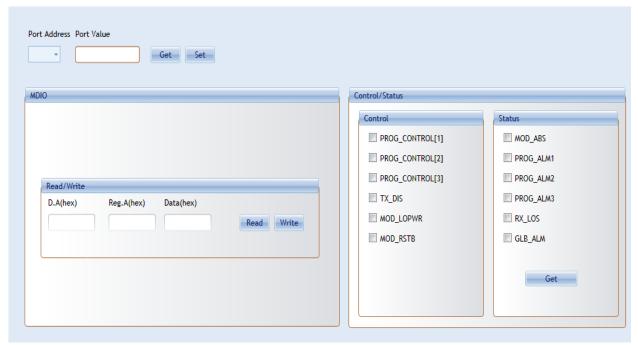

|     | 8.6.   | 5      | Controls                                      |        |              | . 51     |

|     | 8.6.   | 6      | Identification                                |        |              | . 56     |

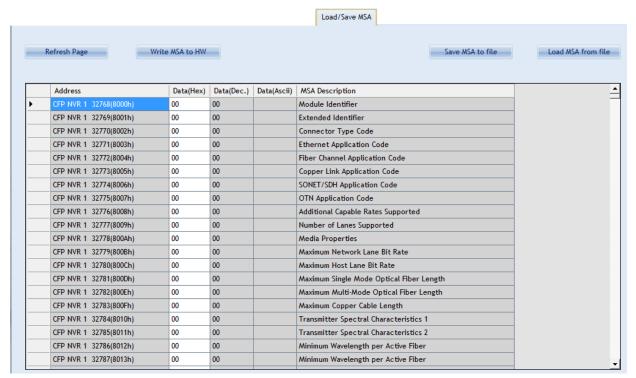

|     | 8.6.   | 7      | Load/Save MSA                                 |        |              | . 65     |

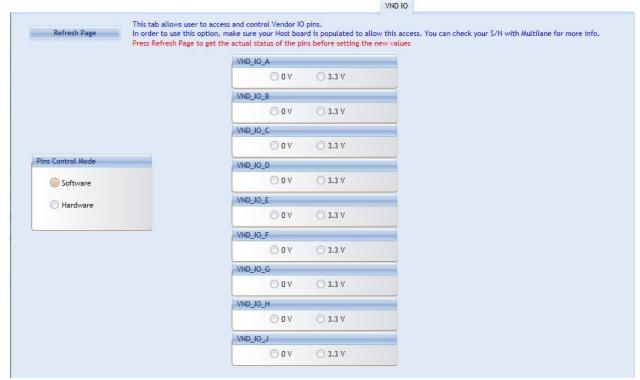

|     | 8.6.   | 8      | CFP Module Vendor I/O pins                    |        |              | . 66     |

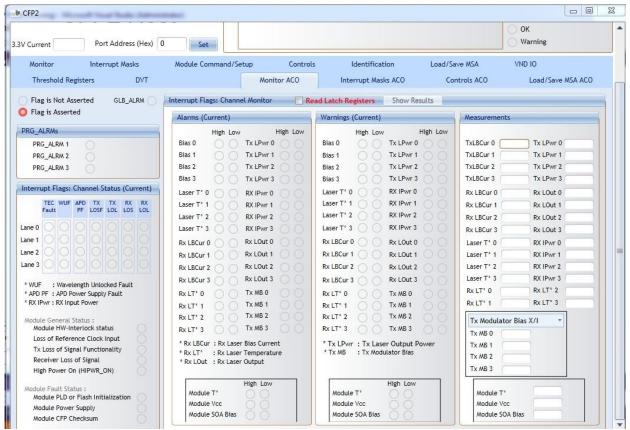

|     | 8.6.   | 9      | Monitor ACO                                   |        |              | . 67     |

|     | 8.6.   | 10     | Interrupt Masks ACO                           |        |              | . 80     |

|     | 8.6.   | 11     | Controls ACO                                  |        |              | . 86     |

|     | 8.6.   | 12     | Load/Save MSA ACO                             |        |              | . 92     |

|     | 8.6.   | 13     | Changing Port Address                         |        |              | . 93     |

|     | 8.6.   | 14     | Additional GUI tabs                           |        |              | . 94     |

| 9.  | ML     | 4028 ( | CFP Break-Out                                 |        | •••••        | 98       |

| Ģ   | 9.1    | Prod   | uct description                               |        |              |          |

|     |        |        |                                               | 9.1.1  | Overview     | 98       |

|     |        |        |                                               | 9.1.2  | Features     | 98       |

|     |        |        |                                               | 9.1.3  | Applications | 98       |

|     | 9.2    | Insta  | Illing the CFP break out module               |        |              |          |

| 10. |        | ъ.     | ML4028-ACO CFP Break-Out                      |        |              |          |

|     | 10.1   | Prod   | uct description                               | 10.1.1 | Overview     | 99<br>99 |

|     |        |        |                                               | 10.1.1 | Features     | 99       |

|     |        |        |                                               | 10.1.2 | Applications |          |

|     |        |        |                                               | TO.T.3 | Applications | コン       |

| multi∟ | ane |

|--------|-----|

|--------|-----|

| 10.2 | Installing the CFP break out module |

|------|-------------------------------------|

| 11.  | Manual Revision History             |

# **List of Figures**

| Figure 1: CFP2 Loop Back                                                                | 14 |

|-----------------------------------------------------------------------------------------|----|

| Figure 2: CFP2 Loop Back Block Diagram                                                  | 17 |

| Figure 3 CFP Initialization sequence                                                    | 19 |

| Figure 4 CFP MDIO Management Frame Structure                                            | 21 |

| Figure 5: USB driver installation.                                                      | 34 |

| Figure 6: USB driver installation Advanced                                              | 34 |

| Figure 7: USB driver location Figure 8: USB driver folder                               | 35 |

| Figure 9: USB driver installation Finish                                                | 35 |

| Figure 10 Communication Window: Main Interface used for initial communication with host | 36 |

| Figure 11 MSA Compliant Startup Sequence                                                | 36 |

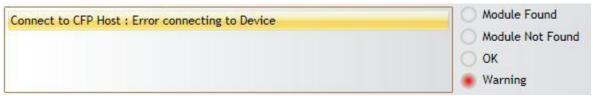

| Figure 12 Communication status box showing a connection error                           | 37 |

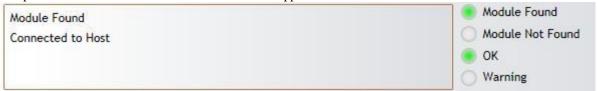

| Figure 13 Communication status box showing successful connection                        | 37 |

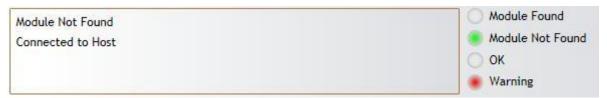

| Figure 14 Communication status box when connected to host but no module is plugged      | 37 |

| Figure 15 GUI tabs                                                                      | 38 |

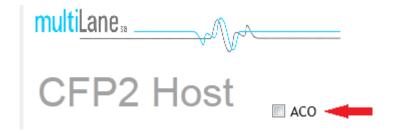

| Figure 16. ACO option                                                                   | 38 |

| Figure 17 Monitor Window                                                                | 39 |

| Figure 18 PRG_ALRMs window                                                              | 40 |

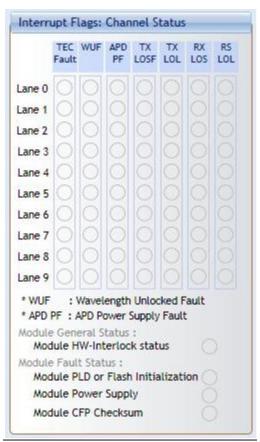

| Figure 19 Interrupt Flags: Channel Status Window                                        | 40 |

| Figure 20 CFP MSA memory map for Network Lane n Fault and Status registers              | 41 |

| Figure 21 Network Lane n Fault and Status corresponding LEDs                            | 41 |

| Figure 22 CFP MSA Module General Status and FAWS Registers                              | 42 |

| Figure 23 Module General Status and Fault corresponding LEDs.                           | 42 |

| Figure 24 Network Lane n Alarm and Warning Registers                                    | 43 |

| Figure 25 Network Lane n Alarms and Warnings LEDs                                       | 43 |

| Figure 26 Module Alarms and Warnings Register                                           | 44 |

| Figure 27 Module Alarms and Warnings LEDs                                               | 44 |

| Figure 28 Measurement window                                                            | 45 |

| Figure 29 Interrupt Masks screen                                                        | 46 |

| Figure 30 Module Command/Setup screen                                                   | 47 |

| Figure 31 CFP MSA PRG_CNTLs Function Select (A005h, A006, A007h) registers              | 48 |

| Figure 32 Programmable Control Functions                                                | 48 |

| Figure 33 CFP MSA PRG_ALRMs Source Select (A008h, A009h, A00Ah) registers               | 49 |

| Figure 34 Programmable Alarm Sources                                                    | 50 |

| Figure 35 Controls Screen                                                               | 51 |

| Figure 36 CFP MSA Module General Control Register A010            | 52 |

|-------------------------------------------------------------------|----|

| Figure 37 CFP MSA Individual Network Lane TX_DIS Control Register | 53 |

| Figure 38 CFP MSA Network Lane TX Control Register                | 54 |

| Figure 39 CFP MSA Network Lane RX Control Register                | 55 |

| Figure 40. CFP MSA Host Lane Control                              | 55 |

| Figure 41 Identification screen.                                  | 56 |

| Figure 42 Load/Save MSA screen                                    | 65 |

| Figure 43. VND IO Tab                                             | 66 |

| Figure 44. Monitor ACO tab                                        | 67 |

| Figure 45. PRG Alarms                                             | 68 |

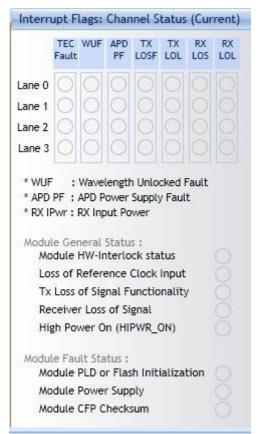

| Figure 46. Interrupt flags: Channel Status (Current)              | 68 |

| Figure 47. Network Lane n Fault and Status (current)              | 69 |

| Figure 48. Module Fault Status (current)                          | 69 |

| Figure 49. CFP MSA Module General Status (current)                | 70 |

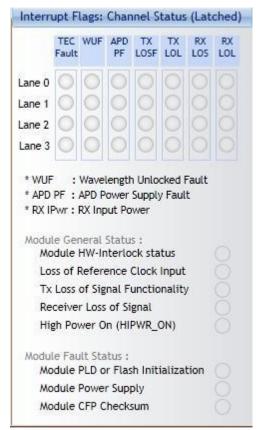

| Figure 50. Interrupt flags: Channel Status (Latched)              | 71 |

| Figure 51. Network Lane n Fault and Status Latch                  | 71 |

| Figure 52. Module General Status Latch                            | 72 |

| Figure 53. Module Fault Status Latch.                             | 72 |

| Figure 54. Network Lane n Alarms and Warnings (Current)           | 73 |

| Figure 55. CFP MSA Network Lane n Alarm and Warning 1             | 74 |

| Figure 56. CFP MSA Network Lane n Alarm and Warning 2             | 74 |

| Figure 57. Network Lane n Alarms and Warnings (Latch)             | 75 |

| Figure 58. CFP MSA Network Lane n Alarm and Warning 1 Latch       | 76 |

| Figure 59. CFP MSA Network Lane n Alarm and Warning 2 Latch       | 76 |

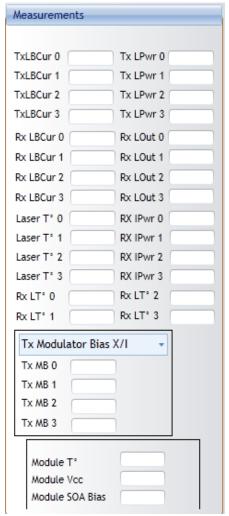

| Figure 60. Measurements                                           | 77 |

| Figure 61. CFP MSA Network Lane A/D Value Measurement Registers   | 79 |

| Figure 62. CFP MSA Module Analog A/D Value Registers              | 80 |

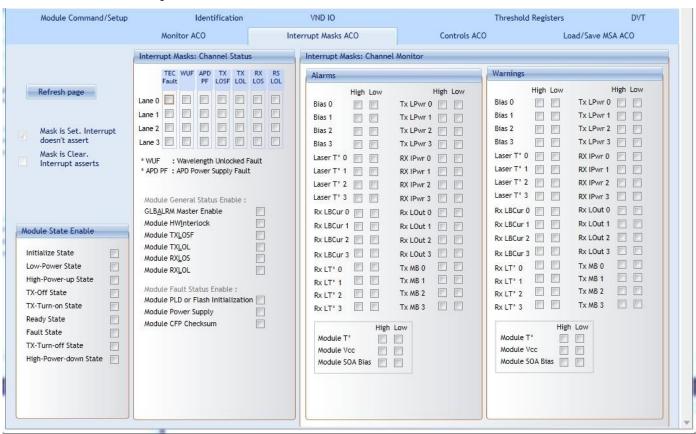

| Figure 63. Interrupt Masks ACO tab                                | 80 |

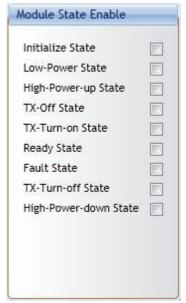

| Figure 64. Module State Enable                                    | 81 |

| Figure 65. CFP MSA Module FAWS Enable Registers                   | 81 |

| Figure 66. Interrupt Masks: Channel Status                        | 82 |

| Figure 67. CFP MSA Network Lane n Fault and Status Enable         | 82 |

| Figure 68. CFP MSA Module General Status Enable                   | 83 |

| Figure 69. CPF MSA Module Fault Status Enable                     | 83 |

| Figure 70. Interrupt Masks: Channel Monitor                       | 84 |

| Figure 71. CFP MSA Network FAWS Enable Registers                  | 85 |

| Figure 72. CFP MSA Module Alarm and Warning 1 Enable      | 86 |

|-----------------------------------------------------------|----|

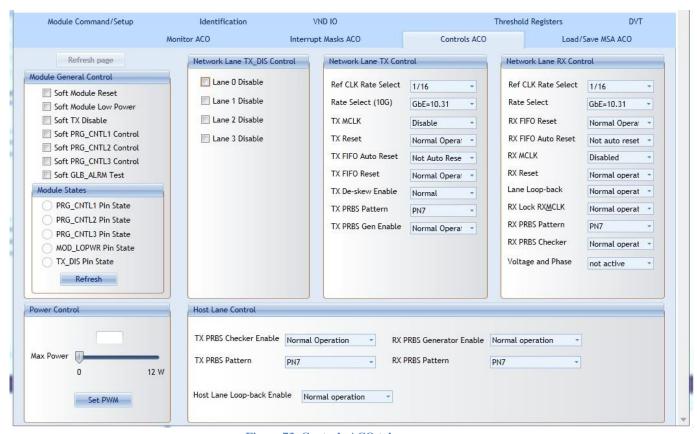

| Figure 73. Controls ACO tab                               | 86 |

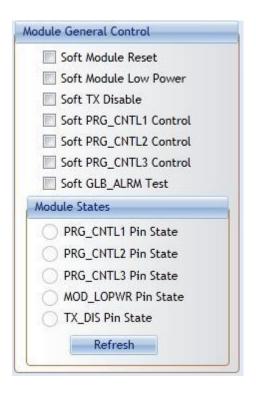

| Figure 74. Module General Control and States              | 87 |

| Figure 75. CFP MSA Module Control Registers.              | 88 |

| Figure 76. CFP MSA Individual Network Lane TX_DIS Control | 88 |

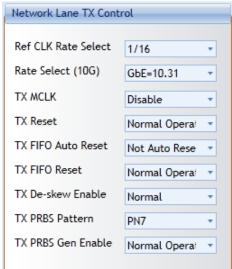

| Figure 77. Network Lane TX Control                        | 88 |

| Figure 78. CFP MSA Netwok Lane TX Control                 | 89 |

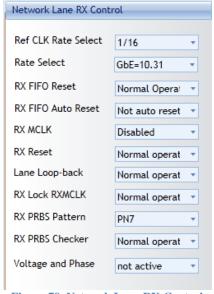

| Figure 79. Network Lane RX Control                        | 89 |

| Figure 80. CFP MSA Network Lane RX Control Registers      | 90 |

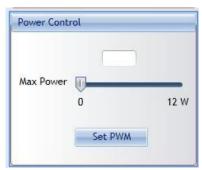

| Figure 81. Power Control.                                 | 90 |

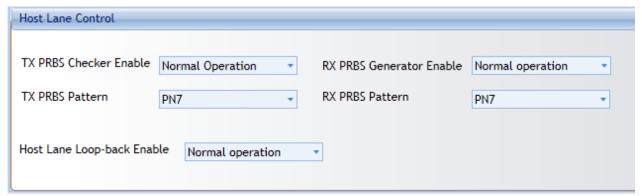

| Figure 82. Host Lane Control.                             | 91 |

| Figure 83. CFP MSA Host Lane Control                      | 91 |

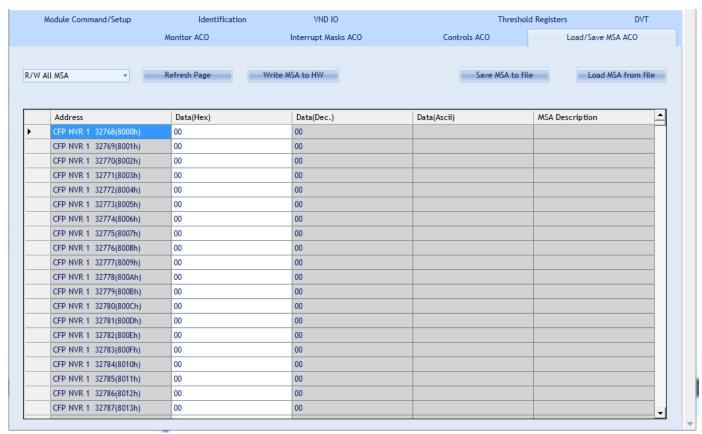

| Figure 84. Load/Save MSA ACO tab                          | 92 |

| Figure 85 GUI Header                                      | 93 |

| Figure 86 Maintenance window                              | 94 |

| Figure 87 Additional tabs                                 | 94 |

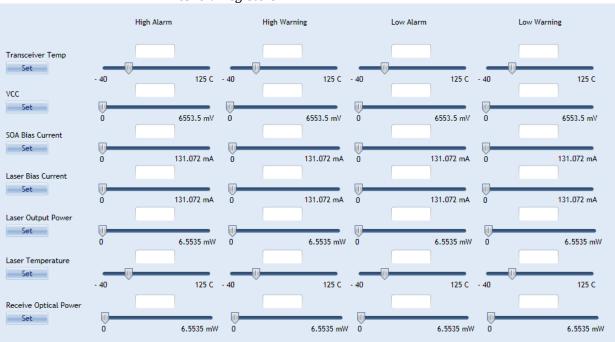

| Figure 88. Threshold registers.                           | 95 |

| Figure 89. Threshold registers MSA memory map             | 96 |

| Figure 90. DVT tab                                        | 97 |

## **List of Tables**

| Fable 1 Recommended Operation Conditions             | 14 |

|------------------------------------------------------|----|

| Γable 2 Recommended Operation Conditions             | 15 |

| Table 3 Recommended Operation Conditions             | 16 |

| Гable 4 MDIO Physical Port Address                   | 20 |

| Table 5. CFP Register Set                            | 22 |

| Table 6. Alarm Sources                               | 23 |

| Table 7: Alarm / Warning Threshold Registers         | 24 |

| Fable 8: Module Temperature Alarms and Warnings      | 24 |

| Fable 9 Module Analog A/D Temperature Value Register | 24 |

| Γable 10 Module Control/State Registers              | 25 |

| Table 11. PWM                                        | 28 |

| Cable 12 PWM                                         | 28 |

## 1. General Safety Summary

CAUTION. This warning symbol means danger. You are in a situation that could cause bodily injury or could result in damage to this product or other property. Before you work on any equipment, be aware of the hazards involved with electrical circuitry and be familiar with standard practices for preventing accidents.

## 2. Required Tools

You need these tools to install the CFP2 transceiver modules:

• Wrist strap or other personal grounding device to prevent ESD occurrences.

## 3. Glossary of Terms/ Acronyms

MSA: Multi Source Agreement. NVR: Non Volatile Registers. NVM: Non Volatile Memory.

## 4. Preface

This is the user manual of the CFP2 Electrical Loopback Modules along with the CFP2 Passive Host Module. It covers the following information:

- The MultiLane CFP MSA values as they are organized in the "CFP MSA Management Interface Specification" data sheet REV1.4.

- Describes the capabilities of the instrument: how to manage its operation.

#### 4.1 About This Manual

This manual is composed of the following sections:

- Getting started introduces you an overview, the features, capabilities, benefits, applications and the reference documents used in the development of this product.

- Recommended Operating Conditions, led indications, a summary and the MSA Memory MAP.

## 5. Products Description

#### 5.1 Overview

Our CFP2 Electrical Loopback is packaged in a standard MSA housing compatible with all CFP2 ports. Used for testing CFP2 transceiver ports, and provides an easy method of servers and blades testing instead of using optical modules. Transmitted data through the host is electrically routed, (internal to the loopback module or through Retimer chip), to the receive data inputs and back to the host.

- It provides an economical way to exercise CFP2 ports during R&D validation, production testing, and field testing.

- The ML4029 provides 4 lanes at 25Gb/s, in retimed loopback mode.

- The ML4043 provides 10 lanes at 10Gb/s, in retimed loopback mode.

- The ML4030 provides 10 lanes at 10Gb/s, in passive loopback mode.

Our 100G CFP2 Compliant Host test boards ML4027 and ML4042 are designed to provide an efficient and easy method of programming and testing CFP2 modules.

The ML4027/ML4042 comes complete with operations software and user manual to enable intuitive testing. As well as designed to simulate an ideal environment for CFP2 module testing. These properties make the host board as electrically transparent as possible, allowing a more accurate assessment of the modules' performance.

The ML4029, ML4043 and ML4030 can be used alone along with the customer Host tool, or with our ML4027/ML4042 CFP2 Hosts to ensure a complete test solution is provided.

## 6. CFP2 Loopback Modules User Guide Manual

## 6.1 ML4029- CFP-2 4x25G Retimed Loopback Module Key Features

- 4 TX & 4 RX Lanes, high-speed signals.

- High performance Signal Integrity traces.

- MSA compliant Digital Diagnostic and Monitoring Interface (DDMI).

- 3 Status LED indicator.

- Built with advanced Rogers™ material.

- Retimed Loop back mode at all 25G Rates.

- PRBS Generator & Detector supports all pattern lengths

- Loss of Signal Detection.

- Programmable output level for receiver sensitivity.

- Temperature sensing.

- Hot Pluggable module.

#### 6.1.1 Benefits

- Economical CFP2 Port Testing

- Custom Memory Maps

- Board Level System Testing

- Retimed Loopback Mode

- BER Capability

#### 6.1.2 LED Indicator

**Green (Solid)** - Signifies that the module is operating in high power permitted mode as defined by the CFP MSA specification.

Amber (Solid) - Signifies the module is operating in low power mode as defined by the CFP MSA specification.

Green/Amber (Blinking) - Signifies that the module is overheated and the temperature high alarm is asserted.

#### 6.1.3 Applications

At Speed Dynamic line card testing.

#### 6.1.4 Operation Conditions

| Parameter             | Symbol  | Notes/Conditions                                                         | Min | Тур | Max | Units |

|-----------------------|---------|--------------------------------------------------------------------------|-----|-----|-----|-------|

| Operating Temperature | $T_{A}$ |                                                                          | 0   |     | 75  | °C    |

| +3.3V Supply Voltage  | VCC     | Main Supply Voltage                                                      |     | 3.3 |     | V     |

| Data Rate             | $R_b$   | Guaranteed to work at 10Gbps per lane, achieving a total rate of 100Gbps |     | 100 |     | Gbps  |

| Power Class           |         |                                                                          |     | 1   |     |       |

**Table 1 Recommended Operation Conditions**

## 6.2 ML4030-CFP-2 10x10G Passive Loopback Module Key Features

- -10 TX & 10 RX Lanes, high-speed signals.

- High performance Signal Integrity traces.

- MSA compliant Digital Diagnostic and Monitoring Interface (DDMI).

- 3 Status LED indicator.

- Built with advanced Rogers<sup>TM</sup> material.

- Temperature sensing.

- Programmable Power Dissipation from 3W to 12 W.

- Hot Pluggable module.

- Cut-off temperature automatically switches the module to low power state to avoid overheating.

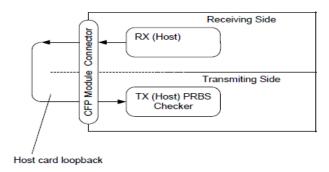

Figure 1: CFP2 Loop Back

#### 6.2.1 Benefits

- Economical CFP2 Port Testing

- Custom Memory Maps

- Board Level System Testing

- Emulates all CFP2 Power classes

#### 6.2.2 LED Indicator

**Green (Solid)** - Signifies that the module is operating in high power permitted mode as defined by the CFP MSA specification.

Amber (Solid) - Signifies the module is operating in low power mode as defined by the CFP MSA specification.

Green/Amber (Blinking) - Signifies that the module is overheated and the temperature high alarm is asserted.

#### 6.2.3 Applications

CFP2 Port Compliance Testing

#### 6.2.4 Operation Conditions

| Parameter             | Symbol  | Notes/Conditions                                                         | Min | Тур | Max   | Units |

|-----------------------|---------|--------------------------------------------------------------------------|-----|-----|-------|-------|

| Operating Temperature | $T_{A}$ |                                                                          | 0   |     | 75    | °C    |

| +3.3V Supply Voltage  | VCC     | Main Supply Voltage                                                      |     | 3.3 |       | V     |

| Data Rate             | $R_{b}$ | Guaranteed to work at 10Gbps per lane, achieving a total rate of 100Gbps |     | 100 |       | Gbps  |

| Power Class           |         |                                                                          |     |     |       | W     |

| Emulates all power    |         |                                                                          |     |     | 3W to |       |

| classes               |         |                                                                          |     |     | 12W   |       |

**Table 2 Recommended Operation Conditions**

## 6.3 ML4043-CFP-2 10x10G Retimed Loopback Module Key Features

- -10 TX & 10 RX Lanes, high-speed signals

- High performance Signal Integrity traces

- MSA compliant Digital Diagnostic and Monitoring Interface (DDMI)

- 3 Status LED indicator

- Built with advanced Rogers<sup>TM</sup> material

- Retimed Loop back mode at all 10G Rates

- Equalizes deteriorated input signals

- provides electrical compensation to cable, copper, and backplane environments to increase system margin and media driving distances

- Input & DFE Adaptation to Optimize Eye opening

- Loss of Signal Detection

- Wide Range CRU

- Programmable output level for receiver sensitivity

- PRBS Checker

- Temperature sensing

- Hot Pluggable module

#### 6.3.1 **Benefits**

- **Economical CFP2 Port Testing**

- **Custom Memory Maps**

- **Board Level System Testing**

- Retimed Loopback Mode

#### 6.3.2 **LED Indicator**

Green (Solid) - Signifies that the module is operating in high power permitted mode as defined by the CFP MSA specification.

Amber (Solid) - Signifies the module is operating in low power mode as defined by the CFP MSA specification.

Green/Amber (Blinking) - Signifies that the module is overheated and the temperature high alarm is asserted.

#### 6.3.3 **Applications**

At Speed Dynamic line card testing.

#### 6.3.4 **Operation Conditions**

| Parameter             | Symbol | Notes/Conditions                                                         | Min | Тур | Max | Units |

|-----------------------|--------|--------------------------------------------------------------------------|-----|-----|-----|-------|

| Operating Temperature | $T_A$  |                                                                          | 0   |     | 75  | °C    |

| +3.3V Supply Voltage  | VCC    | Main Supply Voltage                                                      |     | 3.3 |     | V     |

| Data Rate             | $R_b$  | Guaranteed to work at 10Gbps per lane, achieving a total rate of 100Gbps |     | 100 |     | Gbps  |

| Power Class           |        |                                                                          |     | 1   |     |       |

**Table 3 Recommended Operation Conditions**

#### 6.4 Plugging the CFP2 Loopback module into the Host

**CAUTION.** The CFP2 transceiver module is a static-sensitive device. Always use an ESD wrist strap or similar individual grounding device when handling CFP2 transceiver modules or coming into contact with system

To install a CFP2 transceiver module, follow these steps:

- 1. Attach an ESD wrist strap to yourself on one end and a properly grounded point on the chassis or the rack on the other end.

- 2. The CFP2 transceiver module is located inside its metallic shell.

- 3. Hold the shell so that the identifier label is on the top.

- 4. Align the CFP2 shell in front of the Host module's transceiver socket opening.

- 5. Carefully slide the CFP2 shell into the socket until the transceiver makes contact with the socket electrical connector.

## 6.5 General Description

#### 6.5.1 Overview of CFP management Interface

It is the main communication interface between a Host and a CFP2 module. Host uses the interface to control and monitor the start up, shutdown, and normal operation of the module. This interface operates over a set of hardware pins through the CFP2 module connector and software based protocols (the primary protocol is specified using MDIO bus structure).

The CFP2 loop back device has the following circuit diagram:

Figure 2: CFP2 Loop Back Block Diagram

From a hardware point of view, CFP Management Interface consists of 8 hardware signals: 2 hardware signals of MDC and MDIO, 5 hardware signals of Port Address PRTADR0-4, and 1 hardware signal GLB\_ALRMn. MDC is the MDIO Clock line driven by the Host and MDIO is the bi-directional data line driven by both the Host and module depending upon the data directions.

From a software/protocol point of view, CFP Management Interface consists of the MDIO management frame, a set of CFP registers, and a set of rules for host control, module initialization, and signal exchange between these two.

#### 6.5.2 High Speed Signals

The Electrical High Speed Bus Basically Transfers the TX inputs of the module to the RX outputs, and is either connected in passive loopback mode as in ML4030, or looped back through a retimer chip as in ML4029 and ML4043.

10x10 Modules (ML4030 and ML4043) have a High Speed Bus operating at 10Gb/s.

4x25 Module (ML4029) is capable of operating at speed up to 28Gb/s, Typically the High Speed Bus operates at 25Gb/s.

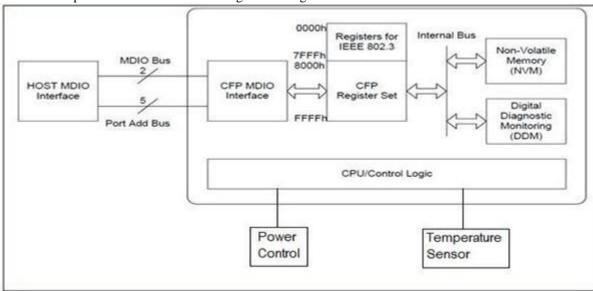

### **6.6** Interface Architecture

A dedicated MDIO logic block in the CFP2 module to handle the high rate MDIO data and a CFP register set that is divided into two register groups, the Non-Volatile Registers (NVR) and the Volatile Registers (VR). The NVRs are connected to a Non-Volatile Memory device for ID/Configuration data storage. Over the internal bus system, the VRs are connected to a device that executes the Host control commands and reports various Digital Diagnostic Monitoring (DDM) data. Note in the rest of this documentation, independent of implementation, CFP registers are also referred as NVRs or VRs.

Our CFP2 module ML4029, ML4030, ML4043 specifications are the following:

- a) Supports of MDC rate up to 4MHz.

- b) CFP Registers at MDIO Device Address 1 as specified by CFP MSA.

- c) Supports various Physical Addresses thus allowing to communicate with many modules plugged in the same Host.

CFP registers use fast memory to shadow the NVM data and the DDM data. The shadow registers decouple the Host-side timing requirements from the module's internal processing, timing, and hardware control circuit introduced latency.

CFP shadow register set meets the following requirements:

- a) It supports dual access from the Host and from module internal operations such as NVM and DDM data transfers.

- b) It supports continuous Host access (read and write) with fast access memory at maximum MDC rate of 4 MHz.

- c) It allows the uploading of NVM content into the CFP register shadow during module initialization. The data saving from CFP register shadow to NVM is supported.

- d) It supports the DDM data update periodically during the whole operation of the module. The maximum data refresh period is 1ms (real time temperature monitoring).

- e) It supports the whole CFP register set including all NVRs and VRs.

- f) Incomplete or otherwise corrupted MDIO bus transactions are purged from memory and disregarded.

- g) The port address is allowed to change in fly without a module reset.

## 7. CFP2 Loopback Modules Functional Description

## 7.1 CFP2 Common Specifications (for ML4029, ML4030 and ML4043)

The Functionalities listed below are common to all Multilane CFP2 loopback modules.

They are implemented and can be used in each of the modules: ML4029, ML4030 and ML4043

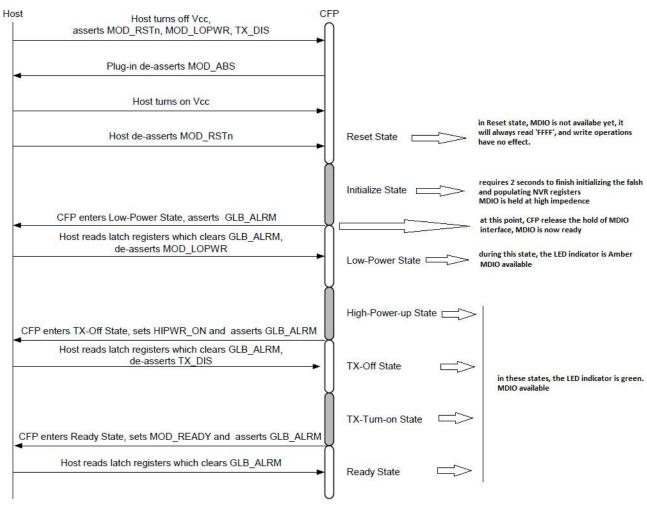

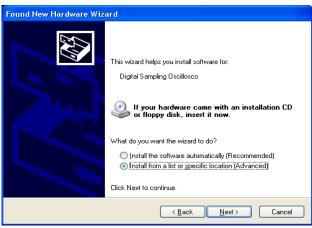

#### 7.1.1 CFP Initialization sequence

This is the Startup sequence for the CFP2 modules:

Figure 3 CFP Initialization sequence

MOD\_RSTs assertion causes CFP2 module to reset, at this stage MDIO interface will be held at high impedance state, the Host will read 'FFFF'h, from any address, while host write operations will have no effect. Upon the deassertion of MOD\_RSTs, CFP2 module exists to initialize state which is a transient state.

**The Initialization time required is 2 seconds.** When Initialization state is done, CFP2 module will enter Low-Power state, at this point MDIO becomes available for R/W operations.

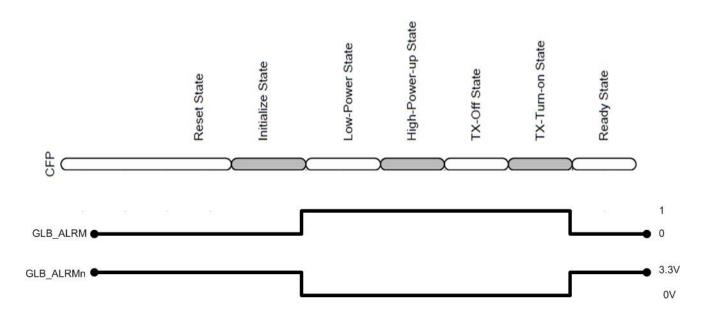

#### **GLB\_ALRM**

Below is the flowchart for GLB\_ALRM signal during CFP states transitions :

GLB \_ALRM is de-asserted during Reset and Initialize state, it is asserted in Low-Power, High-Power-up, Tx-Off and TX-Turn-on states, then de-asserted again when ready state is reached. GLB\_ALRMn is the hardware pin, and is the inverse of GLB\_ALRM.

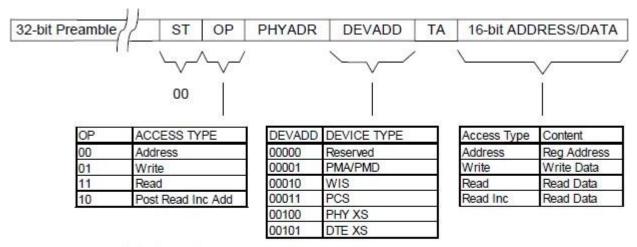

#### 7.1.2 MDIO SIGNALS, addressing and frame structure

As per the port address used, the module will work on any MDIO Physical port address which can be set by the HW input signals PRTADR[2:0]. So when using 2 or more CFP2 slots, each of them can be configured to a different Port Address.

| PRTADR0 | MDIO Physical Port address bit 0 |

|---------|----------------------------------|

| PRTADR1 | MDIO Physical Port address bit 1 |

| PRTADR2 | MDIO Physical Port address bit 2 |

**Table 4 MDIO Physical Port Address**

The MDIO Device Address consists of 5 bits that are sent in MDIO frames, CFP MSA specifies that CFP register Set should be addressed using Device Address = 1.

The Below Frame shows all segments of an MDIO Packet, PHYADR are the 5 bits Physical Address and DEVADD are the 5 bits Device Address.

ST = start bits (2 bits),

OP = operation code (2 bits),

PHYADR = physical port address (5 bits),

DEVADD = MDIO device address (or called device type, 5 bits),

TA = turn around bits (2 bits),

16-bit ADDRESS/DATA is the payload.

**Figure 4 CFP MDIO Management Frame Structure**

#### 7.1.3 CFP Register Set

All registers from 0x8000 to 0x A47F are supported in memory map (Refer to table below), the set of registers starting from 0x8000 to 0x9F00 are implemented as NVR registers, all these registers are always read from NVM during initialization and mapped to corresponding address.

All VR (Volatile Registers) from 0xA000 to 0xA47F are set to zero upon module power up.

The NVR values are saved to NVM by calling the SAVE NVR function. The base ID registers are initially set, but user can change as desired.

|                               |                             |                |                   | CFF                  | Register Allocation                                          |

|-------------------------------|-----------------------------|----------------|-------------------|----------------------|--------------------------------------------------------------|

| Starting<br>Address<br>in Hex | Ending<br>Address<br>in Hex | Access<br>Type | Allocated<br>Size | Data<br>Bit<br>Width | Table Name and Description                                   |

| 8000                          | 807F                        | RO             | 128               | 8                    | CFP NVR 1. Basic ID registers.                               |

| 8080                          | 80FF                        | RO             | 128               | 8                    | CFP NVR 2. Extended ID registers.                            |

| 8100                          | 817F                        | RO             | 128               | 8                    | CFP NVR 3. Network lane specific registers.                  |

| 8180                          | 81FF                        | RO             | 128               | 8                    | CFP NVR 4.                                                   |

| 8200                          | 83FF                        | RO             | 4x128             | N/A                  | MSA Reserved.                                                |

| 8400                          | 847F                        | RO             | 128               | 8                    | Vendor NVR 1. Vendor data registers.                         |

| 8480                          | 84FF                        | RO             | 128               | 8                    | Vendor NVR 2. Vendor data registers.                         |

| 8500                          | 87FF                        | RO             | 6x128             | N/A                  | Reserved by CFP MSA.                                         |

| 8800                          | 887F                        | R/W            | 128               | 8                    | User NVR 1. User data registers.                             |

| 8880                          | 88FF                        | R/W            | 128               | 8                    | User NVR 2. User data registers.                             |

| 8900                          | 8EFF                        | RO             | 12x128            | N/A                  | Reserved by CFP MSA.                                         |

| 8F00                          | 8FFF                        | N/A            | 2x128             | N/A                  | Reserved for User private use.                               |

| 9000                          | 9FFF                        | RO             | 4096              | N/A                  | Reserved for vendor private use.                             |

| A000                          | A07F                        | R/W            | 128               | 16                   | CFP Module VR 1. CFP Module level control and DDM registers. |

| A080                          | A0FF                        | RO             | 128               | 16                   | Reserved by CFP MSA.                                         |

| A100                          | A1FF                        | RO             | 2x128             | N/A                  | Reserved by CFP MSA.                                         |

| A200                          | A27F                        | R/W            | 128               | 16                   | Network Lane VR 1. Network lane specific registers.          |

| A280                          | A2FF                        | R/W            | 128               | 16                   | Network Lane VR 2. Network lane specific registers.          |

| A300                          | A3FF                        | RO             | 2x128             | N/A                  | Reserved by CFP MSA.                                         |

| A400                          | A47F                        | R/W            | 128               | 16                   | Host Lane VR 1. Host lane specific registers.                |

Table 5. CFP Register Set

#### 7.1.4 User NVR Restore and Save Functions (0xA004)

To write permanently to User NVR registers  $(0x8000 \rightarrow 0x9F00)$  Host shall use the "Save" function to store the shadowed data into underlying NVM. The host only needs to perform a single Save operation to copy the entire User NVR shadow registers to the underlying NVM after finishing editing the data.

Upon power-up or reset the User NVR shadow registers are "Restored" with NVM values. Note that the Restore function will overwrite the NVR shadow registers, losing any host-written values in them that have occurred since the last Save to the underlying NVM.

The NVR Access Control Register (A004h) provides the Save function for Host to save the User NVRs content. Bit 5 in NVR Access Control Register is designated for User NVR save command.

A "1" written to bit 5 in register A004h initiates a User NVR Save.

So to call the user NVR save command user can write 0x0020 into register 0xA004.

The Save NVR duration is around 2 seconds. When this function is called it should be followed by a 2 second time wait.

During this process user can't write or read CFP registers.

#### 7.1.5 PRG\_ALRMs

The signals HIPWR\_ON, MOD\_READY, and MOD\_FAULT are CFP internally generated signals and are defaults of the programmable alarm pins PRG\_ALRMx.

The Following Table lists the corresponding functions for each of the PRG\_ALRMs.

| NAME      | ALARM SOURCE                                                    | VALUE                                                           |

|-----------|-----------------------------------------------------------------|-----------------------------------------------------------------|

| HIPWR_ON  | Module high-power-on indicator. PRG_ALRM1 MSA default.          | 0: Module not high powered up 1: Module high power up completed |

| MOD_READY | MOD_READY, module startup sequence done, PRG_ALRM2 MSA default. | 0: Not done<br>1: Done                                          |

| MOD_FAULT | Fault detected. PRG_ALRM3 MSA default.                          | 0: No Fault<br>1: Fault                                         |

**Table 6. Alarm Sources**

#### 7.1.6 Temperature Monitoring

The alarms and warnings of the CFP2 Loop Back are listed in the table 7, 8 and 9. Alarms and Warnings are set in register 0xA01F in bits 8,9,10 and 11, and are continuously asserted and de-asserted when the corresponding alarms/warnings occur. addresses 0x8080, 0x8082, 0x8084, and 0x8086 are reference registers for temperature alarms and warnings, they contain the default values (HA:75, HW:65, LW:5 and LA:0) and can be changed when desired. The module is continuously reading the temperature and storing its value in Register 0x A02F.

When The temperature reaches the High Alarm values, The module front LED indicator will begin blinking.

|             |      |                |     | CFP NVR 2                                  |                                                                                         |               |

|-------------|------|----------------|-----|--------------------------------------------|-----------------------------------------------------------------------------------------|---------------|

| Hex<br>Addr | Size | Access<br>Type | Bit | Register Name<br>Bit Field Name            | Description                                                                             | LSB<br>Unit   |

|             | A1   |                |     | Alarm/Warning Threshold Reg                | gisters                                                                                 |               |

| 8080        | 2    | RO             | 7~0 | Transceiver Temp High Alarm<br>Threshold   | These thresholds are a signed 16-bit integer with LSB = 1/256 of a degree               | 1/256<br>degC |

| 8082        | 2    | RO             | 7~0 | Transceiver Temp High Warning<br>Threshold | Celsius representing a range from -128 to + 127 255/256 degree C. MSA valid             |               |

| 8084        | 2    | RO             | 7~0 | Transceiver Temp Low Warning<br>Threshold  | range is between –40 and +125C." MSB stored at low address, LSB stored at high address. |               |

| 8086        | 2    | RO             | 7~0 | Transceiver Temp Low Alarm<br>Threshold    | Ingii addiess.                                                                          |               |

Table 7: Alarm / Warning Threshold Registers

|              |      |                |       | CFP I                           | Module VR 1                                                  |               |

|--------------|------|----------------|-------|---------------------------------|--------------------------------------------------------------|---------------|

| Hex<br>Addr. | Size | Access<br>Type | Bit   | Register Name<br>Bit Field Name | Description                                                  | Init<br>Value |

| A01F         | 1    | RO             |       | Module Alarms and<br>Warnings 1 |                                                              | 0000h         |

|              |      |                | 15~12 | Reserved                        |                                                              | 0000b         |

|              |      |                | 11    | Mod Temp High Alarm             | Mod temp high Alarm. (FAWS_TYPE_A) 0: Normal, 1: Asserted.   | 0             |

|              |      |                | 10    | Mod Temp High Warning           | Mod temp high Warning. (FAWS_TYPE_A) 0: Normal, 1: Asserted. | 0             |

|              |      |                | 9     | Mod Temp Low Warning            | Mod temp low Warning. (FAWS_TYPE_A) 0: Normal, 1: Asserted.  | 0             |

|              |      |                | 8     | Mod Temp Low Alarm              | Mod temp low Alarm. (FAWS_TYPE_A) 0: Normal, 1: Asserted.    | 0             |

**Table 8: Module Temperature Alarms and Warnings**

|      | \$ # |    | Ø/ : | Module Anal                      | og A/D Value Registers                                                                                                                                                                                                                                                                             |       |

|------|------|----|------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| A02F | 1    | RO | 15~0 | Module Temp Monitor<br>A/D Value | Internally measured temperature in degrees Celsius, a 16-bit signed integer with LSB = 1/256 of a degree Celsius, representing a total range from -128 to + 127 255/256 degC. MSA valid range is between -40 and +125C. Accuracy shall be better than +/- 3 degC over the whole temperature range. | 0000h |

Table 9 Module Analog A/D Temperature Value Register

#### 7.1.7 Insertion Counter

The Insertion counter contains the number of times the module was plugged in a host. The insertion counter is incremented every time the module goes in initializing sequence, as it is nonvolatile it is always saved, and can be read anytime from register 0x8400.

User can clear the insertion counter by writing 0 into 0x8400. The time constraint for this operation is between 1.5 and 1.7 seconds in order to erase the corresponding sector from the flash.

The registers for the insertion counter are as follow:

0x8400 : insertion\_counter (LSB = 1 insertion), representing a counter range from 0 to 255 insertions.

#### 7.1.8 Module Control and Status Registers

The below registers are implemented, and can be checked for module State and Control.

|         | Access<br>Type | Bit  | Bit Field Name         | Description                                                                                                     |

|---------|----------------|------|------------------------|-----------------------------------------------------------------------------------------------------------------|

| 0xA010  |                |      | Module General Control |                                                                                                                 |

| 0221010 | RW             | 14   | Soft Module Low Power  | Register bit for module low power function. 1: Assert.                                                          |

|         | RW             | 13   | Soft TX Disable        | Register bit for TX Disable function. 1: Assert.                                                                |

|         | RW             | 12   | Soft PRG_CNTL3 Control | Register bit for PRG_CNTL3 control function. 1: Assert.                                                         |

|         | RW             | 11   | Soft PRG_CNTL2 Control | Register bit for PRG_CNTL2 control function. 1: Assert.                                                         |

|         | RW             | 10   | Soft PRG_CNTL1 Control | Register bit for PRG_CNTL1 control function. 1: Assert.                                                         |

|         | RW             | 9    | Soft GLB_ALRM Test     | Command bit for software forced test signal. When this bit is asserted it generates GLB_ALRM signal. 1: Assert. |

|         | RO             | 8~6  | Reserved               |                                                                                                                 |

|         | RO             | 5    | TX_DIS Pin State       | Logical state of the TX_DIS pin. 1: Assert.                                                                     |

|         | RO             | 4    | MOD_LOPWR Pin State    | Logical state of the MOD_LOPWR pin. 1: Assert.                                                                  |

|         | RO             | 3    | PRG_CNTL3 Pin State    | Logical state of the PRG_CNTL3 pin. 1: Assert.                                                                  |

|         | RO             | 2    | PRG_CNTL2 Pin State    | Logical state of the PRG_CNTL2 pin. 1: Assert.                                                                  |

|         | RO             | 1    | PRG_CNTL1 Pin State    | Logical state of the PRG_CNTL1 pin.                                                                             |

| 0xA016  |                |      | Module State           |                                                                                                                 |

|         |                | 15~9 | Reserved               |                                                                                                                 |

|         |                | 8    | High-Power-down State  | 1: Corresponding state is active. Word value = 0100h.                                                           |

|         |                | 7    | TX-Turn-off State      | 1: Corresponding state is active. Word value = 0080h.                                                           |

|         |                | 6    | Fault State            | 1: Corresponding state is active. Word value = 0040h.                                                           |

|         |                | 5    | Ready State            | 1: Corresponding state is active. Word value = 0020h.                                                           |

|         |                | 4    | TX-Turn-on State       | 1: Corresponding state is active. Word value = 0010h.                                                           |

|         |                | 3    | TX-Off State           | 1: Corresponding state is active. Word value = 0008h.                                                           |

|         |                | 2    | High-Power-up State    | 1: Corresponding state is active. Word value = 0004h.                                                           |

|         |                | 1    | Low-Power State        | 1: Corresponding state is active. Word value = 0002h.                                                           |

|         |                | 0    | Initialize State       | 1: Corresponding state is active. Word value = 0001h.                                                           |

**Table 10 Module Control/State Registers**

## 7.2 ML4029 CFP2 4x25G Retimed Loopback Additional Functions

The IN012525 from Inphi is used as Retimer chip inside the ML4029, Thus the CFP2 module enables all the Inphi chip capabilities to be applied.

#### 7.2.1 PRBS Generator

All Lanes support the transmission of the following PRBS patterns:

- PRBS 7

- PRBS 9

- PRBS 15

- PRBS 23

- PRBS 31

- 40 bit user defined pattern

- square wave generated pattern

Each lane has its own pattern control register. Generator and checker pattern selections are completely independent.

#### 7.2.2 PRBS Checker

All lanes support pattern locking and error counting of the following PRBS patterns:

- PRBS 7

- PRBS 9

- PRBS 15

- PRBS 23

- PRBS 31

Each lane has its own pattern control register. Generator and checker pattern selections are completely independent.

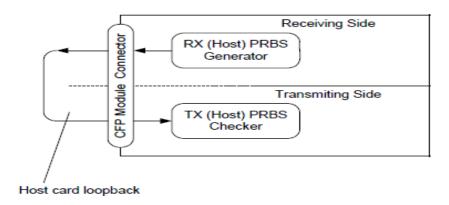

#### 7.2.3 MSA Compliant Host Lane PRBS Control

The above described PRBS Generator and checker can be controlled through MDIO by setting the corresponding CFP registers, thus CFP MSA specifies PRBS generator and error checker for each network lane with CFP register controls. To start a PRBS session, Host shall select the desired PRBS pattern by setting the bits RX PRBS Pattern 1 and RX PRBS Pattern 0 in Host Lane RX Control register (A014h.6~5). The Host enables the PRBS generators by asserting the bit RX PRBS Generator Enable in the same register (A014h.7).

Host shall apply the same operation to Host Lane Control register (A014h.13~12 and A014h.14) correspondingly to set up and enable the PRBS checker. The host side PRBS generator and checker functions shall be stopped by deasserting the RX PRBS Generator Enable and the TX PRBS Checker Enable respectively.

#### 7.2.4 Error Injection

The Lane Pattern control register allows the injection of error bursts into run-time data or PRBS patterns using the custom pattern register to define the burst. Writing one to the error\_insert bit causes a single insertion of an error burst into the transmit data.

Error injection can be used to verify correct operation of error counters.

CFP MSA does not define registers for error injection capability, however this will still be enabled in the ML4029 by giving user direct access to the Inphi registers on the corresponding MDIO address.

#### 7.2.5 EyeScan Capability

The eyescan function provides non destructive asynchronous eyescan, that is valid valid data reception is able to continue during an eyescan.

The eyescan function provides the ability to sample incoming data at phase and voltage offsets to the current ideal sampling position used by the device.

### 7.2.6 Bathtub Curve Measurement

The Inphi chip allows phase shifting of the internal sampling clock allowing the checker to sample data at different phases of the incoming signal, Reading BER at each sampler position accumulates required data to perform a full bathtub curve.

## 7.3 ML4030 CFP2 10x10G Passive Loopback Additional Functions

#### 7.3.1 Programmable Power Dissipation & Thermal Emulation

Register 0x8401 is used for PWM control over MDIO. It is an 8 bit data wide register.

The consumed power changes accordingly when the value in this register is changed (only when in high power mode). In Low power mode the module automatically turns off PWM.

The values written in this register can be stored by calling the Save NVR function, thus the user can permanently change the initial power consumed in high power mode when the module is powered up by setting the register value and calling the Save NVR function.

| Address | Description | Data Range              | Default Value |

|---------|-------------|-------------------------|---------------|

| 0x8401  | PWM         | 0 to 102 (0x00 to 0x66) | 0             |

Table 11. PWM

The PWM can also be used for module thermal emulation.

The module contains a thermal spot that can be heated relative to the related PWM register.

Note that the led starts blinking when the temperature high alarm is reached.

#### 7.3.2 Cut-Off Temperature

To avoid overheating the module, a Cut-Off Temperature is stored in Register 0x8402.

The module is continuously monitoring the temperature and checking its value against the Cut-Off temperature, once reached the module automatically turns off PWM to avoid overheating.

The Default Cut-Off temperature for the ML4030 is 85 degC, so even if the value stored in register 0x8402 is higher than 85 the module will still Cut-Off power at 85 degC, in case the value stored in 0x8402 is lower than 85 then it will be adopted instead of the default value.

| Address | Description         | Data Range              | Default Value |

|---------|---------------------|-------------------------|---------------|

| 0x8402  | Cut-Off Temperature | 0 to 255 (0x00 to 0xFF) | 0x55          |

Table 12. PWM

#### 7.3.3 RX\_LOS

In the ML4030, RX\_LOS is connected to TX\_DIS, so RX\_LOS output is driven by TX\_DIS control, this does not report the actual LOS status of the module since the loopback is passive, but can be used for testing the CFP2 port pins on the host side.

## 7.4 ML4043 CFP2 10x10G Retimed Loopback Additional Functions

The VSC7227 from Vitesse is used as Retimer chip inside the ML4043, Thus the CFP2 module enables all the VSC capabilities to be applied.

#### 7.4.1 Input Equalization

The VSC7227 device features a front end adaptive input equalizer stage. The input signal equalization on the VSC 7227 device helps to combat the Inter Symbol Interference(ISI) of High-speed data as it passes through lossy media. The VSC7277 device provides flexibility in correcting for transmission losses by providing six independent equalization stages.

CFP MSA does not specify registers for such functionality, However it is provided on the ML4043 by providing direct access to the VSC7227 on corresponding MDIO address (address to be defined later).

#### 7.4.2 Input and DFE Adaptation

ML4043 enables optimal compensation of copper losses in backplanes, copper traces and cables, additional control is provided through MDIO interface (Registers to be defined later) to adapt the equalizer settings on the Vitesse for custom signal compensation.

The DFE tap settings on the Vitesse auto adapts to compensate for crosstalk and reflection, custom control is also provided thru MDIO interface for custom adaptation.

#### 7.4.3 Loss of Signal (LOS) Detection

The Receiver Loss of Signal Pin (RX\_LOS) is an output pin to the Host, operating with active-high logic. When asserted, it indicates received power in the CFP2 module is lower than the expected value (RX in this application is considered to be the RX pins of the CFP2 connector, so it is a Host side Loss of Signal Detection).

When the incoming signal strength goes below the programmed threshold value, the LOS signal is asserted.

The corresponding registers specified by CFP MSA are implemented to store the RX\_LOS status for each Host Lane (Registers to be defined later).

#### 7.4.4 Clock Recovery Unit

The VSC7227 device performs clock recovery on the incoming input pins. The recovered clock is used by the data recovery block to regenerate the data by sampling the output of the summing circuit. The data recovery section samples the waveform at the optimal phase and sets the output bit either high or low.

#### 7.4.5 Host Lane PRBS Checker

A PRBS error checker is implemented for each Host lane with CFP register controls. To start a PRBS session, Host shall select the desired PRBS pattern by setting the bits RX PRBS Pattern 1 and RX PRBS Pattern 0 in Host Lane Control register (A014h.6~5).

The Host enables the TX PRBS checker by asserting the bit in Host Lane Control register (A014h.14).

The host side PRBS checker function shall be stopped by de-asserting the TX PRBS Checker Enable respectively.

## 8. ML4027/ML4027-ACO/ML4042 CFP2 Host Programming Manual

#### 8.1 Introduction

This part of the manual describes the key features, the GUI that is used to communicate with the ML4027/ML4042 MSA Compliant CFP2 Host Boards for testing and characterizing any MSA Compliant CFP2 module when plugged into the Host.

In the following context we will be describing the GUI communication with ML4042 having 10 channels, the same concept applies to ML4027 but only 4 channels [3:0] are considered.

#### 8.1.1 Key Features

#### ML4042

- 10 TX & 10 RX Lanes, high-speed signals accessible through 40 SMAs, 18GHz connectors.

- High performance Signal Integrity traces from coax to interface.

- Operates up to 11.2 Gbps per channel

- User Friendly GUI for MDIO control and loading MSA tables.

- CFP Host/ Module Status and control.

- USB controlled.

- MSA compliant Digital Diagnostic and Monitoring Interface (DDMI).

- Status LEDs indicators for signal monitoring and MSA defined Alarms.

- Onboard jumpers for MSA defined control signals.

- Onboard & external reference clock (SMP)

- Built with advanced Rogers<sup>TM</sup> material.

- DCS (de-skew) lane (2 SMP).

#### ML4027

- 4 TX & 4 RX Lanes, high-speed signals accessible through 16 Southwest End Launch Super SMA 27GHz connectors.

- High performance Signal Integrity traces from coax to interface.

- Operates up to 28 Gbps per channel

- User Friendly GUI for MDIO control and loading MSA tables.

- CFP Host/ Module Status and control.

- USB controlled.

- MSA compliant Digital Diagnostic and Monitoring Interface (DDMI).

- Status LEDs indicators for signal monitoring and MSA defined Alarms.

- Onboard jumpers for MSA defined control signals.

- Onboard & external reference clock (SMP)

- Built with advanced Rogers<sup>TM</sup> material.

- DCS (de-skew) lane (2 SMP).

### 8.1.2 Benefits

- Economical CFP2 Port Testing

- Custom Memory Maps

- Board Level System Testing

#### 8.1.3 Applications

Electro-Optical module testing and Characterization

### 8.1.4 Software Capabilities

- CFP Module Status/ Control

- MSA Compliant

- DDMI

#### 8.1.5 Power Requirements

The CFP2 Host module is powered using an external 5V source .

## 8.2 Package Contents

The ML4027/ML4042 product includes the following:

- 1. The CFP2 Passive Host fixture.

- The software package:

One Installer package to automatically install the GUI along with required drivers for the Host.

The GUI runs under Windows XP SP3 (32/64 bits), Vista and Windows 7 OS.

**NOTE.** The CFP2 Host GUI application requires the **Microsoft .NET Framework 4**. If the Microsoft .NET Framework 4 is not existing on your PC, it can be downloaded through this link: http://www.microsoft.com/en-us/download/details.aspx?id=24872

This CFP2 Host software controls the CFP2 Host fixture through USB. The USB drivers will be installed directly with the software installation. In case automatic driver installation failed, you have to install them manually. Please refer to the section USB Driver installation on Windows XP.

Remember to connect the PC to the fixture through a usb cable.

## 8.3 Installation

#### 8.3.1 USB Driver Installation on Windows XP

- Power on the CFP2 Host fixture.

- Plug-in the USB cable into the PC and connect it to the CFP2 Host fixture.

- The following window will pop up.

- Choose the "No, not this time" option, and then click "Next".

Figure 5: USB driver installation

• Choose "Install from a list or specific location (Advanced)", and then click "Next".

Figure 6: USB driver installation Advanced

- Choose "Search for the best driver in these locations".

- Check the choice: "Include this location in the search".

- Browse for the subfolder: "CFP Host" existing in "MultiLane Drivers" folder in the installation path. Choose it and then click "Ok".

- Click "Next".

Figure 7: USB driver location

Figure 8: USB driver folder

When this window appears, click "Finish". The USB driver is now installed.

Figure 9: USB driver installation Finish

#### **8.5** Communication Window

| Initialize | Refresh | Pause Monitor | About Us | Autolog          |

|------------|---------|---------------|----------|------------------|

|            |         |               |          | Module Found     |

|            |         |               |          | Module Not Found |

|            |         |               |          |                  |

|            |         |               |          | OK               |

Figure 10 Communication Window: Main Interface used for initial communication with host

The Initialize button is the application's main entry point, used to establish a connection with the CFP2 Host board and the Module. Once a USB connection is established, the Host checks if a CFP2 Module is inserted, and accordingly illuminates the corresponding (Module Found or Module Not Found) LED. If a CFP2 Module is inserted, the initialization process proceeds with the MSA compliant startup sequence for the module as shown in the diagram below:

Figure 11 MSA Compliant Startup Sequence

Hence, the CFP2 module goes through Reset, Initialize, High-Power up, TX-Off, TX-Turn-on states, and finally enters the Ready state. During this sequence, the CFP2 module sets INIT\_DONE, asserts GLB\_ALRM, HIPWR\_ON, and MOD\_READY signals sequentially. These signals inform host the completion of control circuit initialization and MDIO availability, module fully powered up, and module ready for data, respectively. OK LED will be asserted when the module startup sequence is complete.

Next, the status box window in the GUI will show any success or failure messages that are being returned as a result of the GUI communicating or attempting to communicate with the hardware.

Figure 12 Communication status box showing a connection error

The above figure shows a typical connection error when a connection attempt with the host fails. The default Error Status format is: [funtion]: [returned error].

The picture below shows how the status box should appear after a successful connection.

Figure 13 Communication status box showing successful connection

Figure 14 Communication status box when connected to host but no module is plugged

Please note that the status box messages are always shown with the most recent message on top. You can check the "Autolog" check box for activating the silent logging mode. In this mode, a log file will be automatically generated, and all software steps will be logged during runtime and is useful for debugging purposes when communicating with Multilane applications engineering support.

Refresh button: checks for connection status, refresh Hardware Readings and updates GUI

Pause Monitor button: Pause/Resume monitoring.

About Us button: shows program information (name, version) and company information.

# 8.6 Graphical User Interface Section

The GUI for the CFP2 host board contains 13 sections giving the user the ability to monitor, customize, control and configure the Hardware.

| Monitor            | Interrupt Masks | Module Command/Setup | Controls    | Identification      | Load/Save MSA | VND IO            |

|--------------------|-----------------|----------------------|-------------|---------------------|---------------|-------------------|

| Threshold Register | rs DVT          |                      | Monitor ACO | Interrupt Masks ACO | Controls ACO  | Load/Save MSA ACO |

Figure 15 GUI tabs

As shown in Figure 15 above, the GUI contains the following main tabs:

- ✓ Monitor/Monitor ACO: Monitoring interface allowing the user to check the Hardware operation.

- ✓ Interrupt Masks/Interrupt Masks ACO: Allows the user to select which FAWS bits to contribute to GLB ALRM.

- ✓ **Module Command/Setup**: Allows the user to control module behavior.

- ✓ **Controls/Controls ACO**: Provides both additional and alternative controls to hardware pins and programmable control pins in controlling CFP2 module.

- ✓ **5-Identification:** Shows module Base ID Registers.

- ✓ 6-Load-Save MSA/Load-Save MSA ACO: Save the current CFP2 configuration to a file, or load existing configuration from file and map it to MSA memory.

- ✓ **7-VND IO:** Provides control for CFP Vendor IO pins.

As noticed, this GUI supports both ML4027 CFP2 Host and ML4027-ACO CFP2-ACO Host.

To enable ACO mode, the user should check the below ACO Checkbox. When it's checked, the related tabs are shown and the unrelated tabs are hidden.

Figure 16. ACO option

#### 8.6.1 Monitor

Figure 17 Monitor Window

### **Digital Diagnostic Monitor:**

The Monitor Window shown in Figure 16 above is the main source of the module status and alarm/warning flags conditions. It shows the current status of a flag, the default flag update rate is 2 Hz, so the flag status is updated every 0.5 seconds.

#### Flag Status:

- Flag is not asserted: the corresponding LED is OFF (Transparent).

- Flag is asserted: the corresponding LED is ON (Red).

The Monitor window shows 3 different sections:

- 1- PRG ALRMs

- 2- Interrupt Flags: Channel Status

- 3- Interrupt Flags: Channel Monitor

#### 8.6.1.1 PRG\_ALRMS

| PRG_ALRMs  |   |

|------------|---|

| PRG_ALRM 1 | 0 |

| PRG_ALRM 2 | Ō |

| PRG_ALRM 3 | Ō |

Figure 18 PRG\_ALRMs window

PRG\_ALRM1, PRG\_ALRM2 and PRG\_ALRM3 are programmable alarm pins that can be programmed with custom alarm sources. When the custom select alarm is enabled, the corresponding LED is asserted on the monitor screen. Please refer to section 3.3-II for information about how to set a custom alarm source for PRG\_ALRMs.

### 8.6.1.2 Interrupt Flags: Channel Status

Figure 19 Interrupt Flags: Channel Status Window

### *I- Network Lane n Fault and Status*

| A210 | 16 | RO |      | Network Lane n Fault and Status | 16 registers, one for each network lane, represent 16 network lanes. n = 0, 1,, N-1. N_max = 16. Actual N is module dependent. | 0000h |

|------|----|----|------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-------|

|      |    |    | 15   | Lane TEC Fault                  | 0: Normal; 1: Asserted. (FAWS_TYPE_B)                                                                                          | 0     |

|      |    |    | 14   | Lane Wavelength Unlocked Fault  | 0: Normal; 1: Asserted. (FAWS_TYPE_C)                                                                                          | 0     |

|      |    |    | 13   | Lane APD Power Supply Fault     | 0: Normal; 1: Asserted. (FAWS_TYPE_B)                                                                                          | 0     |

|      |    |    | 12~8 | Reserved                        |                                                                                                                                | 0     |

|      |    |    | 7    | Lane TX_LOSF                    | 0: Normal; 1: Asserted. (PMD)<br>(FAWS_TYPE_C)                                                                                 | 0     |

|      |    |    | 6    | Lane TX_LOL                     | 0: Normal; 1: Asserted. (Network) (FAWS_TYPE_B)                                                                                | 0     |

|      |    |    | 5    | Reserved                        |                                                                                                                                | 0     |

|      |    |    | 4    | Lane RX_LOS                     | 0: Normal; 1: Asserted. (FAWS_TYPE_B)                                                                                          | 0     |

|      |    |    | 3    | Lane RX_LOL                     | 0: Normal; 1: Asserted. (FAWS_TYPE_B)                                                                                          | 0     |

|      |    |    | 2~0  | Reserved                        |                                                                                                                                | 000b  |

Figure 20 CFP MSA memory map for Network Lane n Fault and Status registers

|        | TEC<br>Fault | WUF | APD<br>PF | TX<br>LOSF | TX<br>LOL | RX<br>LOS | RS<br>LOL |

|--------|--------------|-----|-----------|------------|-----------|-----------|-----------|

| Lane 0 | 0            | 0   | 0         |            |           |           |           |

| Lane 1 | 0            | 0   | 0         |            |           |           |           |

| Lane 2 | 0            | 0   | 0         |            |           |           |           |

| Lane 3 | 0            | 0   | 0         | 0          |           |           |           |

| Lane 4 | 0            | 0   | 0         | 0          |           |           |           |

| Lane 5 | 0            | 0   | 0         |            | 0         |           |           |

| Lane 6 | 0            | 0   | 0         | 0          |           |           |           |

| Lane 7 | 0            | 0   | 0         | 0          | 0         |           |           |

| Lane 8 | 0            | 0   | 0         |            |           |           |           |

| Lane 9 | 0            | 0   | 0         |            |           |           |           |

Figure 21 Network Lane n Fault and Status corresponding LEDs

The above picture shows the status LEDs of the flags shown in Figure 19. When a flag is asserted, the corresponding LED is illuminated red.

### **II- Module Fault and Status**

|      |   |    |      | Module FAWS Re                    | gisters                                                                                                                                                                                                                                                                        |       |

|------|---|----|------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|